Compiler Optimizations for Power Aware Computing

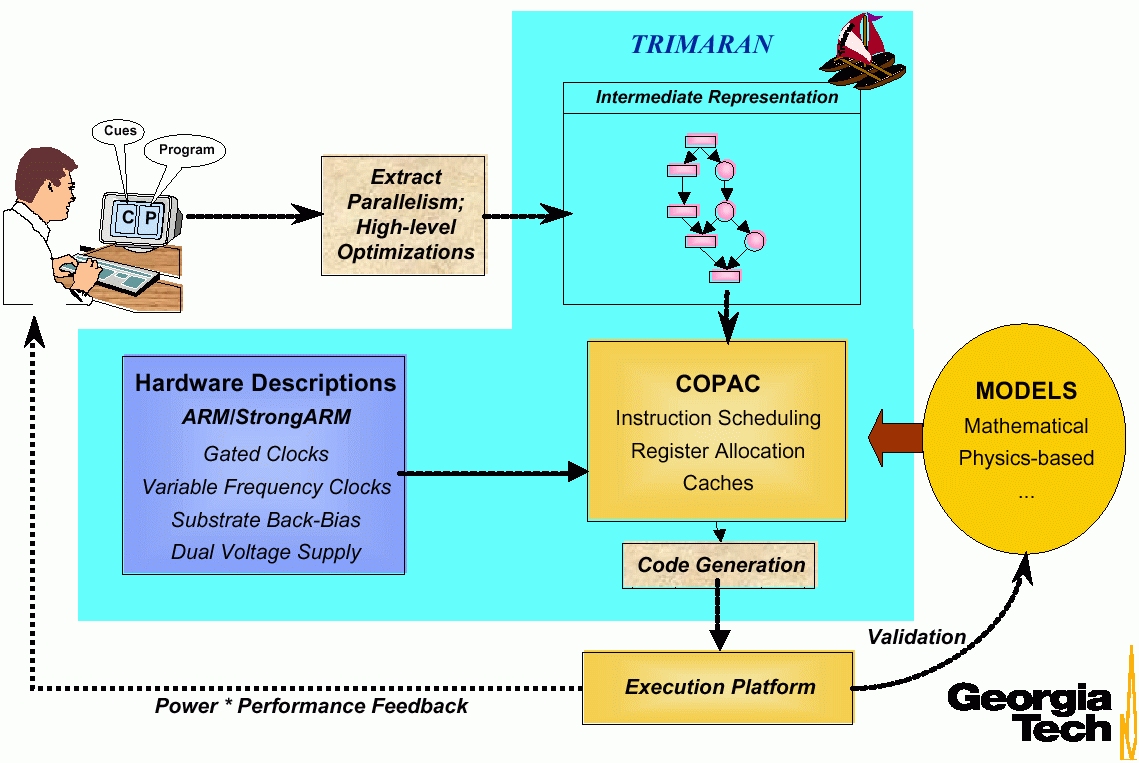

The main research emphasis of the Low Power group is Power Aware Computing. Currently the group is working on Compiler Optimizations for power minimization, using "TRIMARAN", a compiler infrastructure for research.

Project Overview

The focus of our proposed effort is on software techniques for application-managed power-aware computing .Thus ,in our setting , challenge applications will be instrumented, transformed and optimized so as to meet the specified constraints in the power-performance spectrum.Our efforts will be focussed on trading quality-of-service (QoS) metrics such as precision and performance in favor of power, and vice-versa. We are focussing on the following :

Algorithm based transformations for power

An algorithm-based transformer will decompose computations in such a way that the total energy required to perform an algorithm with specified bounds will be met by the best QoS possible , along other dimensions.Models of algorithm behavior built ,as seen through the compiler and the operating system will help explore the space of trade-offs.A significant contribution of our proposed effort involves developing such models and validating them.These models will also be used by several other phases of our proposed research.For example the compiler optimizations that we propose to innovate ( below ) are performed statically , and hence rely heavily on the development of empirical and/or physics-based mathematical models that we will be innovating , to help determine the power/energy needed to produce a specified performance goal.

Optimizing compiler based techniques for power-aware computing

Innovating a range of compiler optimizations based on instruction scheduling , loop transformations including loop-invariant code motion , register and memory hierarchy optimizations , and others help find solutions satisfying the power-QoS expectations ,is at the heart of our proposed research.Annotationsor constraints embedded in the source or application being developed will be used to guide the programmer specified QoS constraints including power.Also , compiler transformations that exploit energy optimizing technology features such as gated clocks variable power supply and threshold voltage logic and variable frequency clocks will be developed and validated on simulation models and strong ARM architecture in collaboration with Intel.In this mode , we envision compiler driven dynamic modulation of the hardware/technology features for power/energy minimization.Preliminary experiments using the FFT and software pipelining have shown that power*performance can be improved 33 %.

Power models of instructions and instruction sequences

We will develop empirical parametrized power models of individual instructions and instruction sequences in terms of supply voltage ,technology parameters such as threshold voltage , instruction delay / timing / clock speed and input data values ( best- , worst- , avg- case ) These will be developed in collaboration with the industry and validated with laboratory power measurements.

TECHNICAL COLLABORATORS:

FACULTY:

STUDENTS:

Publications

J. Park, V. Mooney and P. Pfeiffenberger, "Sleepy Stack Reduction in Leakage Power," Proceedings of the International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS'04), pp.148-158, September 2004. Presentation (pdf)

O. Celebican, T. Simunic Rosing and V. Mooney, "Energy Estimation of Peripheral Devices in Embedded Systems," Proceedings of the 2004 ACM Great Lakes Symposium on VLSI (GLVLSI'04), pp.430-435, April 2004. Poster (pdf)

J. C. Park, V. Mooney and S. K. Srinivasan, " Combining data remapping and voltage/frequency scaling of second level memory for energy reduction in embedded systems," Microelectronics Journal, 34(11), pp. 1019-10241, November 2003.

J. C. Park, V. Mooney, K. Palem and K. W. Choi,"Energy Minimization of a Pipelined Processor using a low Voltage Pipelined Cache," Conference Record of the 36th Annual Asilomar Conference on Signals, Systems and Computers (ASILOMAR'02), pp. 67-73, November 2002. Presentation (pdf)

K. Puttaswamy, K. W. Choi, J. C. Park, V. Mooney, A. Chatterjee and Peeter Ellervee, "System Level PowerPerformance TradeOffs in Embedded Systems Using Voltage and Frequency Scaling of OffChip Buses and Memory," Proceedings of the International Symposium on System Synthesis (ISSS'02), pp. 225-230, October 2002. Presentation (pdf)

S. K. Srinivasan, J. C. Park and V. Mooney, "Combining Data Remapping and Voltage/Frequency Scaling of Second Level Memory for Energy Reduction in Embedded Systems," Proceedings of the First International Workshop on Embedded System Codesign (ESCODES'02), pp. 57-62, September 2002. Presentation (pdf)

K. Palem, R. Rabbah, P. Korkmaz, V. Mooney and K. Puttaswamy, "Design Space Optimization of Embedded Memory Systems via Data Remapping," Proceedings of the Languages, Compilers, and Tools for Embedded Systems (LCTES'02), pp. 28-37, June 2002. Presentation (pdf)

K. Puttaswamy, L. N. Chakrapani, K. W. Choi, Y. S. Dhillon, U. Diril, P. Korkmaz, K. K. Lee, J. C. Park, A. Chatterjee, P. Ellervee, V. Mooney, K. Palem and W. F. Wong, " Power-Performance Trade-Offs in second level memory used by an ARM-Like RISC Architecture," in the book Power Aware Computing, edited by Rami Melhem, University of Pittsburgh, PA, USA and Robert Graybill, DARPA/ITO, Arlington, VA, USA, published by Kluwer Academic/Plenum Publishers, pp. 211-224, May 2002.

L. N. Chakrapani, P. Korkmaz, V. J. Mooney III, K. V. Palem, K. Puttaswamy and W. F. Wong"The Emerging Power Crisis in Embedded Processors: What can a (poor) Compiler do?," Proceedings of the International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES'01), pp. 176-180, November 2001. Presentation (pdf)

Technical Reports

P. Pfeiffenberger, J. Park and V. Mooney, "Some Layouts Using the Sleepy Stack Approach," Technical Report GIT-CC-04-05, Georgia Institute of Technology, June 2004.

R. Banakar, M. Ekpanyopang, K. Puttaswamy, R. Rabbah, M. Balakrishnan, V. Mooney and K. Palem, "An Access based Energy Model for the Datapath and Memory Hierarchy of HPL-PD Microarchitecture in Trimaran Framework (TRIREME)," Technical Report GIT-CC-02-35, Georgia Institute of Technology, June 2002.

P. Korkmaz, K. Puttaswamy and V. Mooney, "Energy Modeling of Processor Core and Memory Hierarchy using Synopsys and Kamble and Ghosh Model," CREST Technical Report CREST-TR-02-002, Georgia Institute of Technology, February 2002.

Reference Web Sites

Last Update : September 2004