# Basics of Energy & Power Dissipation

Lecture notes S. Yalamanchili, S. Mukhopadhyay and A. Chowdhary

#### Georgia Tech

# Outline

- Basic Concepts

- Dynamic power

- Static power

- Time, Energy, Power Tradeoffs

- Activity model for power estimation

- Combinational and sequential logic

(2)

# Reading

- <a href="http://en.wikipedia.org/wiki/CPU">http://en.wikipedia.org/wiki/CPU</a> power dissipation

- <a href="http://en.wikipedia.org/wiki/CMOS#Power: switching a nd leakage">http://en.wikipedia.org/wiki/CMOS#Power: switching a nd leakage</a>

- <a href="http://www.xbitlabs.com/articles/cpu/display/core-i5-2500t-2390t-i3-2100t-pentium-g620t.html">http://www.xbitlabs.com/articles/cpu/display/core-i5-2500t-2390t-i3-2100t-pentium-g620t.html</a>

- http://www.cpu-world.com/info/charts.html

- Goal: Understand

- The sources of power dissipation in combinational and sequential circuits

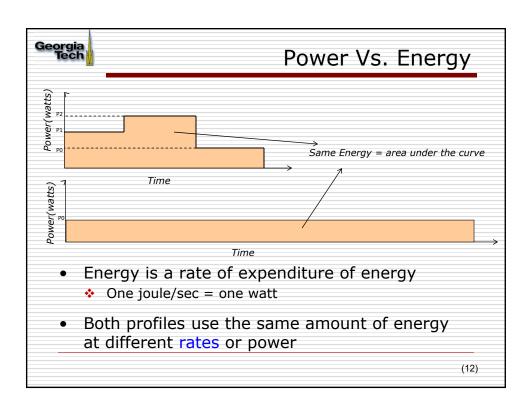

- Power vs. energy

- Options for controlling power/energy dissipation

(3)

#### Georgia Tech

#### Where Does the Power Go in CMOS?

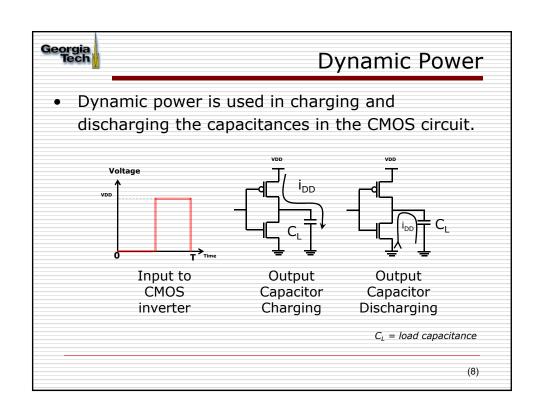

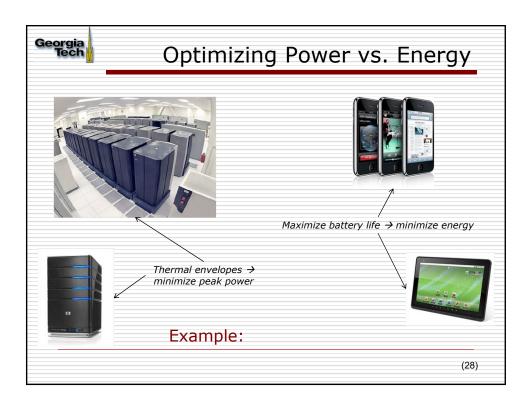

- Dynamic Power Consumption

- ❖ Caused by switching transitions → cost of switching state

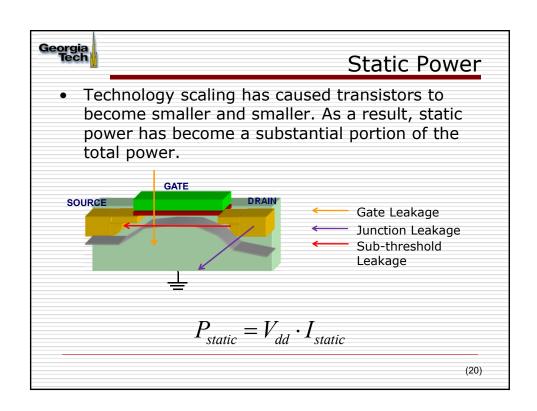

- Static Power Consumption

- Caused by leakage currents in the absence of any switching activity

- Power consumption per transistor changes with each technology generation

- No longer reducing at the same rate

- What happens to power density?

(4)

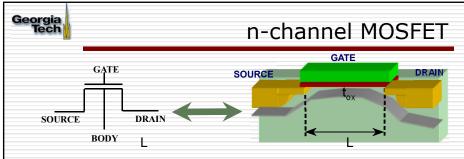

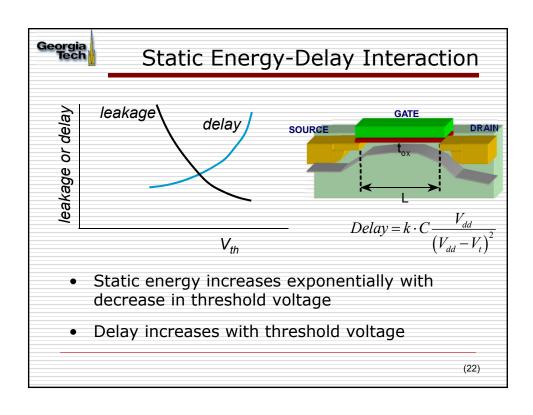

- $V_{qs} < V_t$  transistor off  $V_t$  is the threshold voltage

- $V_{gs} > V_t$  transistor on

- · Impact of threshold voltage

- $\bullet$  Higher  $V_t$ , slower switching speed, lower leakage

- Lower V<sub>t</sub>, faster switching speed, higher leakage

- Actual physics is more complex but this will do for now!

(5)

#### Georgia Tech

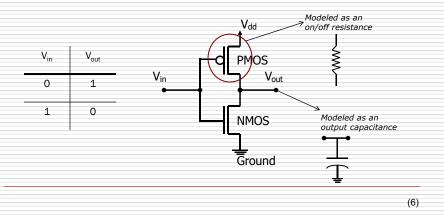

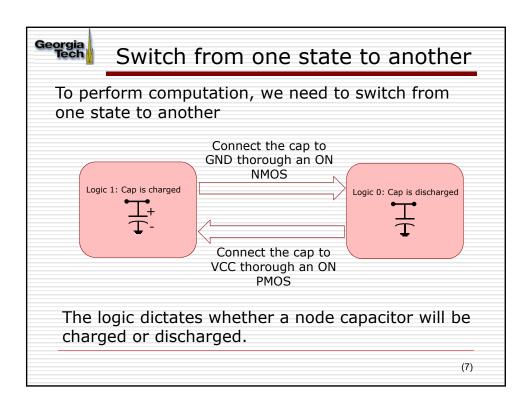

# **Abstracting Energy Behavior**

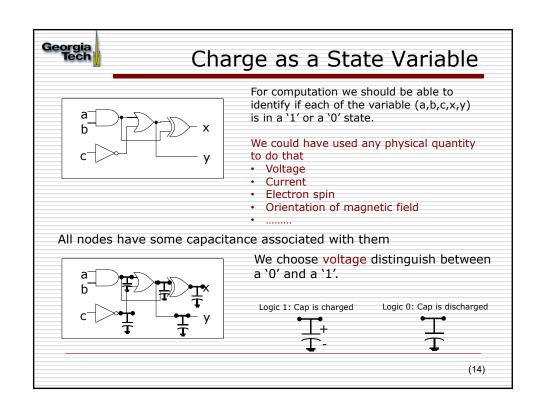

- How can we abstract energy consumption for a digital device?

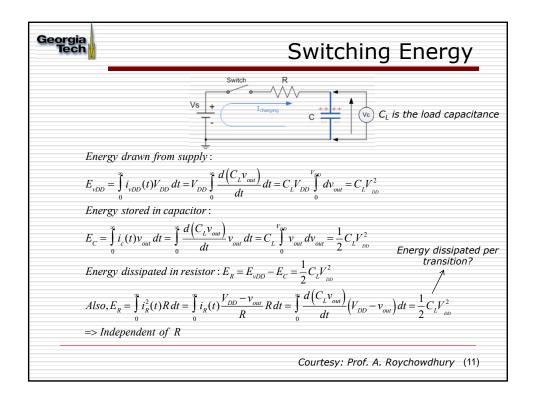

- Consider the energy cost of charge transfer

#### Dynamic Power vs. Dynamic Energy Dynamic power: consider the rate at which switching (energy dissipation) takes place Voltage $i_{DD}$ Input to Output Output **CMOS** Capacitor Capacitor inverter Charging Discharging activity factor = fraction of total capacitance that switches each cycle $Delay = k \cdot C \frac{V_{dd}}{\left(V_{dd} - V_{t}\right)^{3}}$ $V_{dd} \cdot V_{dd} \cdot F$ (13)

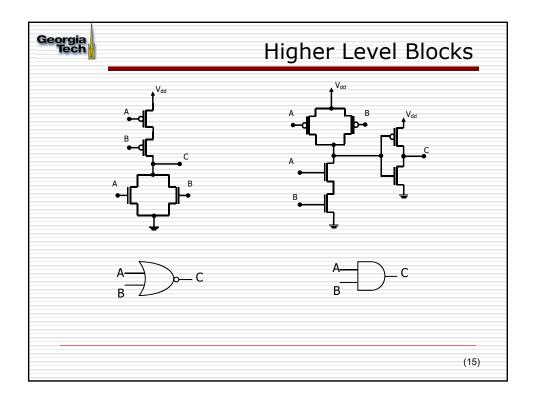

# Gate Power Dissipation

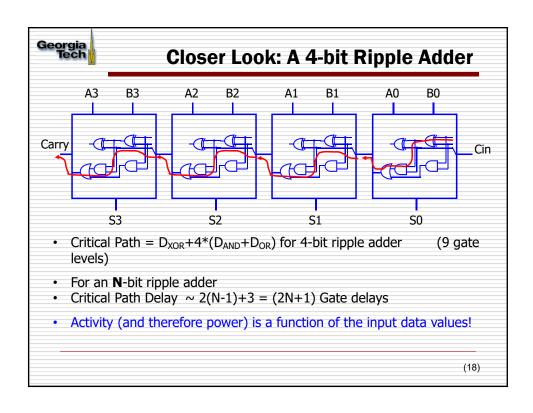

- Switching activity depends on the input pattern and combinational logic

- Consider a  $0\rightarrow 1$  transition on the output of a gate

$$\begin{array}{ccc} p_0 \times p_1 \\ \hline \text{Probability gate} & \text{Probability gate} \\ \text{output was 0} & \text{output is 1} \end{array}$$

$$p_0 = \frac{N_0}{2^n}$$

$p_1 = \frac{N_1}{2^n}$

$$p_1 = \frac{N_1}{2^n}$$

$N_0$  = number of 0's in the truth table

Example:

(16)

## Temperature Dependence

As temperature increases static power increases<sup>1</sup>

$$I_{leakage} = F(Temp)$$

<sup>1</sup>J. Butts and G. Sohi, "A Static Power Model for Architects, MICRO 2000

(23)

#### Georgia Tech

# The World Today

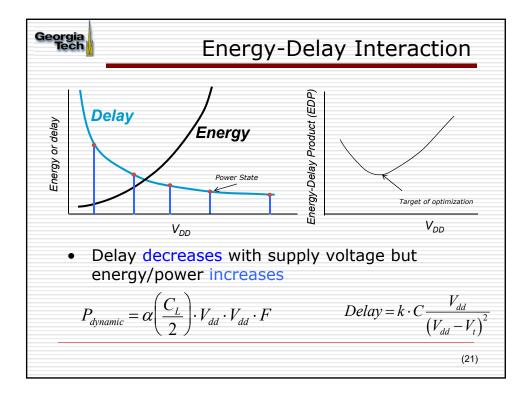

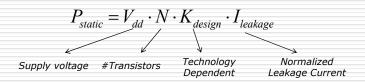

Yesterday→ scaling to minimize time (max F)

$$P_{dynamic} = \alpha \left(\frac{C_L}{2}\right) \cdot V_{dd} \cdot V_{dd} \cdot F \qquad Delay = k \cdot C \frac{V_{dd}}{\left(V_{dd} - V_t\right)^2}$$

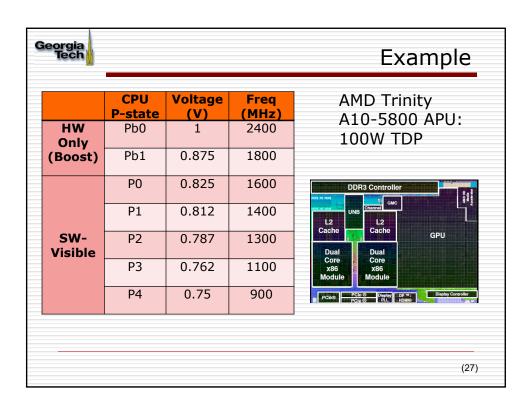

- Maximum performance (minimum time) is too expensive in terms of power

- ❖ Imaging scaling voltage by 0.7 and frequency by 1.5 → how does dynamic power scale?

- Today: trade/balance performance for power efficiency

(24)

#### Factors Affecting Power

- Transistor size

- $\diamond$  Affects capacitance  $(C_L)$

- Rise times and fall times (delay)

- Affects short circuit power (not in this course)

- Threshold voltage

- Affects leakage power

- Temperature

- Affects leakage power

- Switching activity

- Frequency (F) and number of switching transistors ( $\alpha$ )

$$P_{dynamic} = \alpha \left(\frac{C_L}{2}\right) \cdot V_{dd} \cdot V_{dd} \cdot F \qquad Delay = k \cdot C \frac{V_{dd}}{\left(V_{dd} - V_t\right)^2}$$

(25)

#### Georgia Tech

# Low Power Design: Options?

$$P_{dynamic} = \alpha \left(\frac{C_L}{2}\right) \cdot V_{dd} \cdot V_{dd} \cdot F \qquad Delay = k \cdot C \frac{V_{dd}}{\left(V_{dd} - V_t\right)^2}$$

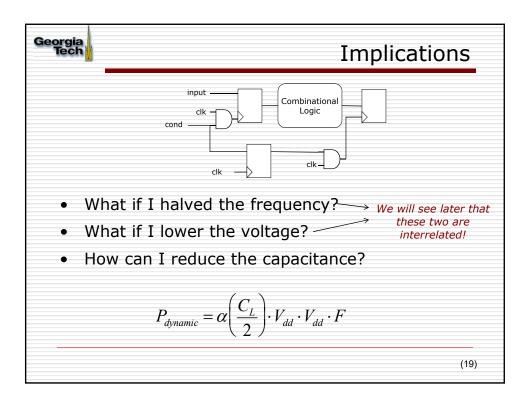

- Reduce V<sub>dd</sub>

- Increases gate delay

- Note that this means it reduces the frequency of operation of the processor!

- Compensate by reducing threshold voltage?

- Increase in leakage power

- Reduce frequency

- Computation takes longer to complete

- Consumes more energy (but less power) if voltage is not scaled

(26)

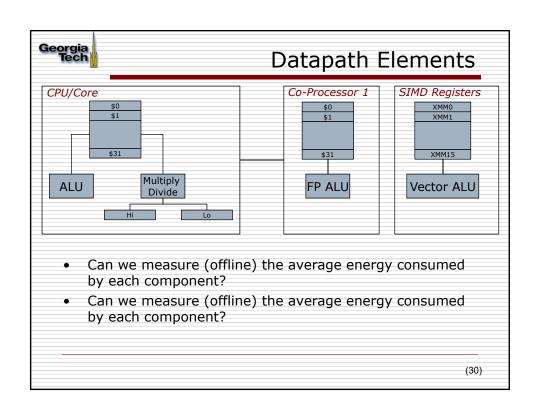

#### Georgia Tech Modeling Component Energy · Per-use energies can be estimated from Gate level designs and analyses Circuit-level designs and analyses · Implementation and measurement There are various open-source tools for analysis · Mentor, Cadence, Synopsys, etc. Hardware Estimation Circuit-level Design Results: Estimation Area, Energy, Technology Tool Timing, etc. **Parameters** (29)

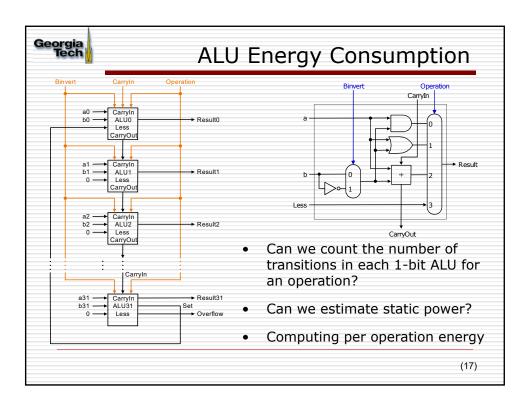

# Simple Power Model for Processors

- Per instruction energy measurements

- Permits a software model of energy consumption of a program

- Execution time use to assess power requirements

- A first order model of energy consumption for software

- A table of energy consumption per instruction

- More on this later!

(31)

#### Georgia Tech

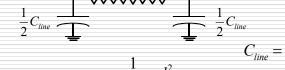

#### What About Wires?

Lumped RC Model

$R_{line} = r \cdot l$ Resistance per unit length

Capacitance per

- We will not directly address delay or energy expended in the interconnect in this class

- Simple architecture model: lump the energy/power with the source component

(32)

#### Summary

- Two major classes of energy/power dissipation

static and dynamic

- Managing energy is different from managing power → leads to different solutions

- Technology plays a major role in determining relative costs

- Energy of components are often estimated using approximate models of switching activity

(33)

#### Georgia Tech

#### Study Guide

- Explain the difference between energy dissipation and power dissipation

- Distinguish between static power dissipation and dynamic power dissipation

- What is the impact of threshold voltage on the delay and energy dissipation?

- As you increase the supply voltage what is the behavior of the delay of logic elements? Why?

- As you increase the supply voltage what is the behavior of static and dynamic energy and static and dynamic power of logic elements?

(34)

## Study Guide (cont.)

- Do you expect the 0-1 and 1-0 transitions at the output of a gate to dissipate the same amount of energy?

- For a mobile device, would you optimize power or energy? Why? What are the consequences of trying to optimize one or the other?

- Why does the energy dissipation of a 32-bit integer adder depend on the input values?

- If I double the processor clock frequency and run the same program will it take less or more energy?

(35)

#### Georgia Tech

#### Study Guide (cont.)

- When the chip gets hotter, does it dissipate more or less energy? Why?

- How can you reduce dynamic energy of a combinational logic circuit?

- How can you reduce static energy of a combinational logic circuit?

(36)

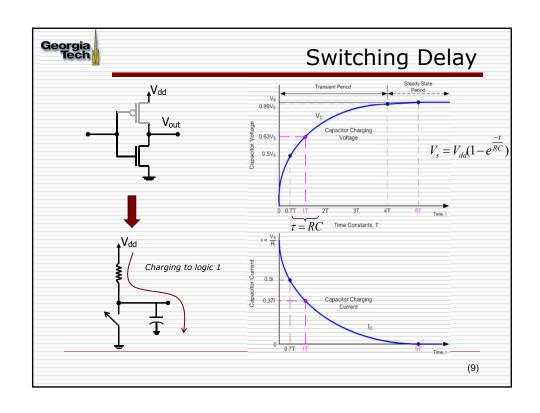

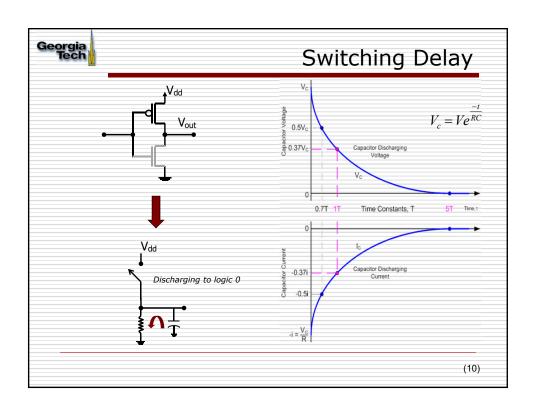

# Dynamic Energy Dynamic Power Load capacitance Static Energy Static Power Glossary Time constant Threshold voltage Switching delay Switching energy Static Power