Publications (as of October 2023)

DISCLAIMER

WARNING: This directory contains pdf/ps files of articles that may be covered by copyright. You may browse the articles at your convenience, (in the same spirit as you may read a journal or a proceeding article in a public library). Retrieving, copying, distributing these files may violate the copyright protection law. We recommend that the user abides by U.S. and international law in accessing this directory.

Theses Supervised

Yu-Cheng Chen, “Cyber Threat Propagation Modeling In Cyber Physical Systems,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Spring 2022. Presentation (pdf)

Taimour Webhe, “ Medical Device Security Through Hardware Signatures,”Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Fall 2018. Presentation (pdf)

Jun Cheol Park, “Sleepy Stack: a New Approach to Low Power VLSI and Memory,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Summer 2005. Presentation (pdf)

Yudong Tan, “Cache Design and Timing Analysis for Preemptive Multi-tasking Real-Time Uniprocessor Systems,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Spring 2005. Presentation (pdf)

Jaehwan Lee, “Hardware/Software Deadlock Avoidance for Multiprocessor Multiresource System-on-a-Chip,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Fall 2004. Presentation (pdf)

Kyeong Keol Ryu, “Automated Bus Generation for Multiprocessor SoC Design,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Summer 2004. Presentation (pdf)

Tankut Akgul, “Assembly Instruction Level Reverse Execution for Debugging,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Spring 2004. Presentation (pdf)

Pramote Kuacharoen, “Embedded Software Streaming via Block Streaming,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Spring 2004. Presentation (pdf)

Bilge E. S. Akgul, “The System-on-a-Chip Lock Cache,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Spring 2004. Presentation (pdf)

Eung Seo Shin, “Automated Generation of Round-robin Arbitration and Crossbar Switch Logic,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Fall 2003. Presentation (pdf)

Mohamed A. Shalan, “Dynamic Memory Management for Embedded Real-Time Multiprocessor System-on-a-Chip,” Ph.D. dissertation, Georgia Institute of Technology, Atlanta, Fall 2003. Presentation (pdf)

Thesis

V. Mooney, “Hardware/Software Codesign of Run-Time Systems,” Technical Report CSL-TR-98-762, Stanford Computer Science Department Electronic Library, June 1998.

Books

R. Reis, V. Mooney and P. Hasler, editors, VLSI-SoC: Advanced Topics on Systems on a Chip, Springer Science+Business Media: New York, 2008.

M. Glesner, R. Reis, L. Indrusiak, V. Mooney and H. Eveking, editors, VLSI-SoC: From Systems to Chips, Springer Science+Business Media: New York, 2006.

Journals/Book Chapters

Y. Chen, V. Mooney and S. Grijalva, “Grid Cyber-Security Strategy in an Attacker-Defender Model,” MDPI Journal of Cryptography, (Special Issue on Feature Papers on Hardware Security), 5(2), 12, April 2021.

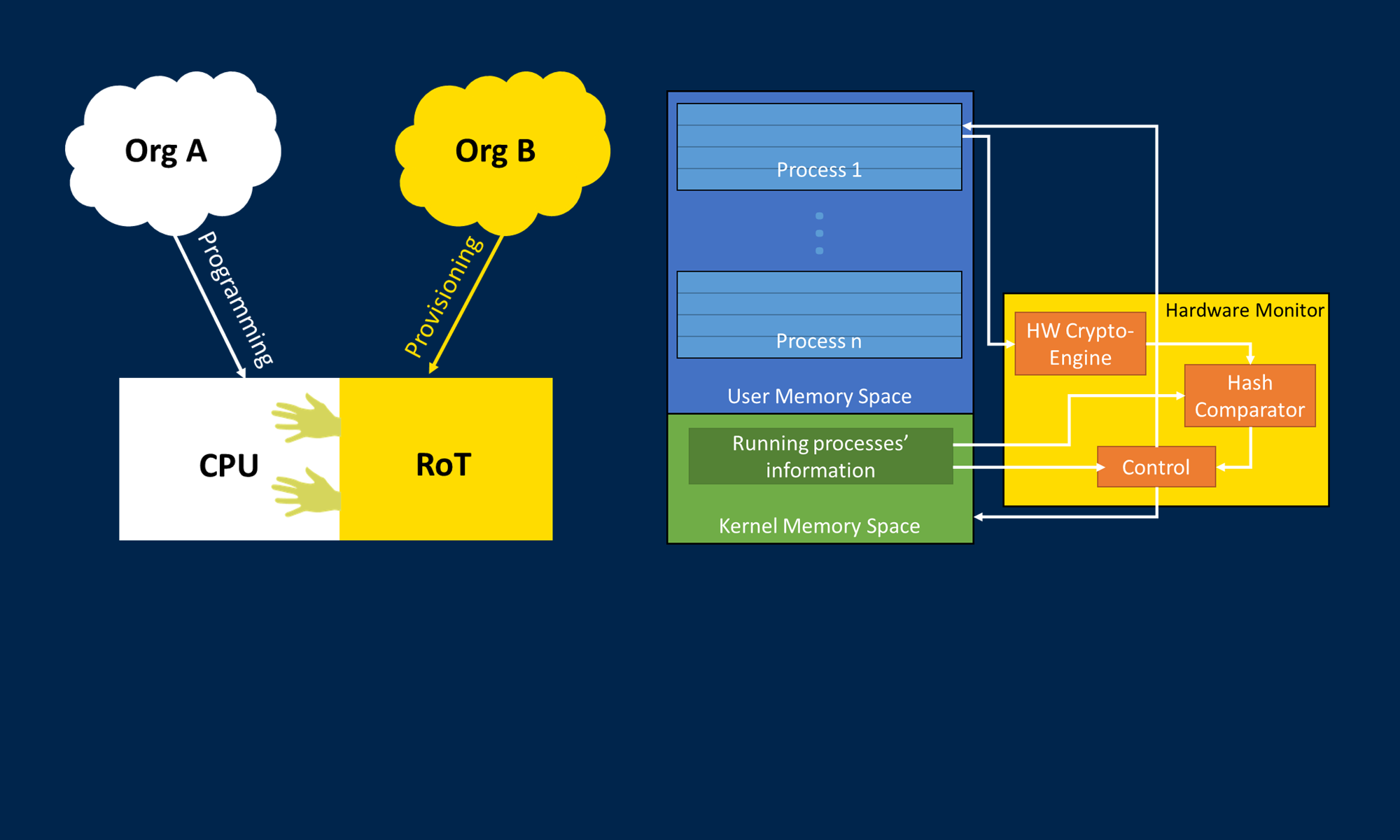

P. Coppock, M. Yacoub, B. Qin, A. Daftardar, Z. Tolaymat and V. Mooney, “Hardware Root-of-Trust-based Integrity for Shared Library Function Pointers in Embedded Systems,” Microprocessors and Microsystems (Special Issue on Embedded Computing – MECO 2019), 79, 103270, November 2020.

T. Wehbe, V. Mooney and D. Keezer, “Hardware-Based Run-Time Code Integrity in Embedded Devices,” MDPI Journal of Cryptography (Special Issue on Physical Layer Security and Trust for Legacy Systems and Supply Chain Assurance), 2(3), 20, August 2018.

T. Wehbe, V. Mooney, O. Inan and D. Keezer, “Securing Medical Devices Against Hardware Trojan Attacks Through Analog-, Digital-, and Physiological-Based Signatures,” Journal of Hardware and Systems Security (Special Issue on Hardware Solutions for Cyber Security), June 2018.

C. Dhoot, L.P. Chau, S.R. Chowdhury and V. Mooney, “Low Power Motion Estimation Based on Probabilistic Computing,”IEEE Transactions on Circuits and Systems for Video Technology (TCSVT), 24(1), pp. 1-14, January 2014.

A. Singh, A. Basu, K.V. Ling and V. Mooney, “Models for Characterizing Noise Based PCMOS Circuits,” ACM Transactions on Embedded Computing Systems, 13(1s), November 2013.

J.C. Park and V. Mooney, “Pareto Points in SRAM Design Using the Sleepy Stack Approach,” in the book VLSI-SoC: From Systems to Silicon, edited by Ricardo Reis, Adam Osseiran and Hans-Joerg Pfleiderer, published by Springer Science+Business Media: New York, pp. 163-177, 2007.

J. Lee and V. Mooney, “A Novel O(n) Parallel Banker’s Algorithm for System-on-a-Chip,” IEEE Transactions on Parallel and Distributed Systems, 17(12), 1377-1389, December 2006.

J.C. Park and V. Mooney, “Sleepy Stack Leakage Reduction,” IEEE Transactions on VLSI, 14(11), 1250-1263, November 2006.

J. Lee and V. Mooney, “Hardware/Software Partitioning of Operating Systems: Focus on Deadlock Avoidance,” Chapter 4 in the book System On Chip: Next Generation Electronics, edited by Bashir M. Al-Hashimi, IEE, United Kingdom, 2006.

J. Lee and V. Mooney, “ An O(min(m,n)) Parallel Deadlock Detection Algorithm,” ACM Transactions on Design Automation of Electronic Systems, 10(3), 573-586, July 2005.

J. Lee and V. Mooney, “Hardware/Software Partitioning of Operating Systems: Focus on Deadlock Detection and Avoidance,” IEE Proceedings on Computers and Digital Techniques, 152(2), pp. 167-182, March 2005.

P. Kuacharoen, V. Mooney and V. Madisetti, “Stream-Enabled File I/O for Embedded Systems,” KMITL Science Journal, Special Issue International Symposium on Mathematical, Statistical and Computer Sciences, 5(1), pp. 62-75, February 2005.

K. Ryu and V. Mooney, “Automated Bus Generation for Multiprocessor SoC Design,”

IEEE Transactions on Computer-Aided Design of Integrated Circuits

and Systems (TCAD), 23(11), pp. 1531-1549, November 2004.

T. Akgul and V. Mooney, “Assembly Instruction Level Reverse Execution for Debugging,” ACM Transactions on Software Engineering and Methodology (TOSEM), 13(2), pp. 149-198, April 2004.

J.C. Park, V. Mooney and S. Srinivasan, “Combining Data Remapping and Voltage/Frequency Scaling of Second Level Memory for Energy Reduction in Embedded Systems,” Microelectronics Journal, 34(11), pp. 1019-1024, November 2003.

V. Mooney, “Hardware/Software Partitioning of Operating Systems,” in the book Embedded Software for SoC, edited by Ahmed Amine Jerraya, Sungjoo Yoo, Diederik Verkest and Norbert Wehn, published by Kluwer Academic Publishers, Boston, MA, U.S.A, pp. 187-206, September 2003.

P. Kuacharoen, V. Mooney and V. Madisetti, “Software Streaming via Block Streaming,” in the book Embedded Software for SoC, edited by Ahmed Amine Jerraya, Sungjoo Yoo, Diederik Verkest and Norbert Wehn, published by Kluwer Academic Publishers, Boston, MA, U.S.A, pp. 435-448, September 2003.

V. Mooney and D. Blough, “A Hardware-Software Real-Time Operating System Framework for SOCs,” IEEE Design and Test of Computers, pp. 44-51, November-December 2002.

B. E. S. Akgul and V. Mooney, “The System-on-a-Chip Lock Cache,” International Journal of Design Automation for Embedded Systems, 7(1-2), pp. 139-174, September 2002.

K. Puttaswamy, L. Chakrapani, K. Choi, Y. Dhillon, U. Diril, P. Korkmaz, K. Lee, J.C. Park, A. Chatterjee, P. Ellervee, V. Mooney, K. Palem and W. Wong, “Power-Performance Trade-Offs in Second Level Memory Used by an ARM-Like RISC Architecture,” in the book Power Aware Computing, edited by Rami Melhem, University of Pittsburgh, PA, USA and Robert Graybill, DARPA/ITO, Arlington, VA, USA, published by Kluwer Academic/Plenum Publishers, pp. 211-224, May 2002.

V. Mooney and G. De Micheli, “Hardware/Software Codesign of Run-Time Schedulers for Real-Time Systems,”Design Automation of Embedded Systems, 6(1), pp. 89-144, September 2000.

W. Shields Neely and V. Mooney, “System Level Design for System on a Chip,” Design Automation of Embedded Systems, 3(4), pp. 291-309, September 1998.

Conference/Workshop Proceedings

J. Keller, S. Paul, K. Hutto, S. Grijalva and V. Mooney, “Developing Simulation Capabilities for Supply Chain Cybersecurity of the Electricity Grid,” 2023 IEEE PES Innovative Smart Grid Technologies Latin America (ISGT-LA’23), pp. 205-209, November 2023.

K. Hutto and V. Mooney, “Late Breaking Results: COPPER: Computation Obfuscation by Producing Permutations for Encoding Randomly,” 2023 60th Design Automation Conference (DAC 60), July 2023.

Y. Tan, A. Diwakar, J. Jagielo and V. Mooney, “Software Compilation Using FPGA Hardware: Register Allocation,” 2023 12th Mediterranean Conference on Embedded Computing (MECO’23), June 2023. Presentation (pdf)

J. Keller, S. Paul, S. Grijalva and V. Mooney, “Experimental Setup for Grid Control Device Software Updates in Supply Chain Cyber-Security,” 2022 54th North American Power Symposium (NAPS’22), October 2022. Presentation (pdf)

Best Paper Award: K. Hutto, S. Grijalva and V. Mooney, “RanCompute: Computational Security in Embedded Devices via Random Input and Output Encodings,” 2022 11th Mediterranean Conference on Embedded Computing (MECO’22), June 2022. Presentation (pdf)

K. Hutto, S. Paul, B. Newberg, V. Boyapati, Y. Vunnam, S. Grijalva and V. Mooney, “PUF-Based Two-Factor Authentication Protocol for Securing the Power Grid Against Insider Threat,” Kansas Power and Energy Conference (KPEC’22), April 2022. Presentation (pdf)

B. Newberg, S. Grijalva and V. Mooney, “Open-Source Architecture for Multi-Party Update Verification for Data Acquisition Devices,” Power and Energy Conference at Illinois, March 2022. Presentation (pdf)

K. Hutto, S. Grijalva and V. Mooney, “Hardware-Based Randomized Encoding for Sensor Authentication in Power Grid SCADA Systems,” 2022 Texas Power and Energy Conference, February 2022. Presentation (pdf)

S. Paul, Y. Chen, S. Grijalva and V. Mooney, “A Cryptographic Method for Defense Against MiTM Cyber Attack in the Electricity Grid Supply Chain,” 2022 IEEE PES Innovative Smart Grid Technologies Conference (ISGT’22), pp. 1-5, February 2022.

B. Semiz, M. Emre Gursoy, M. Hasan Shandhi, L. Orlandic, V. Mooney and O. Inan, “Automatic Subject Identification Using Scale-Based Ballistocardiogram Signals,” EAI Mobihealth 2021, November 2021.

K. Hutto and V. Mooney, “Sensing with Random Encoding for Enhanced Security in Embedded Systems,” 2021 10th Mediterranean Conference on Embedded Computing (MECO’21), pp. 809-814, June 2021. Presentation (pdf)

Y. Chen, V. Mooney and S. Grijalva, “Electricity Grid Cyber-Physical Security Risk Assessment Using Simulation of Attack Stages and Physical Impact,” Kansas Power and Energy Conference (KPEC’20), July 2020.

Y. Chen, V. Mooney and S. Grijalva, “Grid Cyber-Security Strategy Assessment in an Attacker-Defender Model,” IEEE Power Systems Conference (PSC’20), March 2020.

Y. Chen, V. Mooney and S. Grijalva, “A Survey of Attack Models for Cyber-Physical Security Assessment in Electricity Grid,” Proceedings of the IFIP Working Group 10.5 Very Large Scale Integration System-on-a-Chip (VLSI-SoC 2019), October 2019.

G. Lopez, M. Foreman, A. Daftardar, P. Coppock, Z. Tolaymat and V. Mooney, “ Hardware Root-of-Trust Based Integrity for Shared Library Function Pointers in Embedded Systems,” 2019 8th Mediterranean Conference on Embedded Computing (MECO’19), pp. 196-201, June 2019.

Y. Chen, D. Campbell, V. Mooney, S. Grijalva, B. Eames, A. Outkin, E. Vugrin, R. Helinski and B. Anthony, “Power Grid Bad Data Injection Attack Modeling in PRESTIGE,” Government Microcircuit Applications and Critical Technology Conference (GOMACTech’19), Albuquerque, NM, March 2019.

Y. Chen, T. Gieseking, D. Campbell, V. Mooney and S. Grijalva, “A Hybrid Attack Model for Cyber-Physical Security Assessment in Electricity Grid,”in Texas Power and Energy Conference (TPEC), Feb. 2019.

T. Wehbe, V. Mooney and D. Keezer, “Work-in-Progress: A Chip-Level Security Framework for Assessing Sensor Data Integrity,” in International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), Oct. 2018.

V. Chukwuka, Y. Cheng, S. Grijalva and V. Mooney, “ Bad Data Injection Attack Propagation in Cyber-Physical Power Delivery Systems,”in Power System Conference (PSC), Sep. 2018.

T. Wehbe, V. Mooney, D. Keezer, O. Inan and A. Javaid, “Use of Analog Signatures for Hardware Trojan Detection,” Proceedings of the 14th FPGAworld Conference (FPGAworld’17), ACM, Sept. 2017, pp. 15-22.

T. Wehbe, V. Mooney, A. Javaid and O. Inan “A Novel Physiological Features-Assisted Architecture for Rapidly Distinguishing Health Problems from Hardware Trojan Attacks and Errors in Medical Devices,” IEEE International Symposium on Hardware Oriented Security and Trust (HOST’17), May 2017, pp. 106-109.

T. Wehbe, V. Mooney, D. Keezer and N. Parham “A Novel Approach to Detect Hardware Trojan Attacks on Primary Data Inputs,” Proceedings of the 2015 ACM Workshop on Embedded Systems Security (WESS’15), Article 2, 10 pages, October 2015. Presentation (pdf)

A. Gbade-Alabi, D. Keezer, V. Mooney, A. Poshmann, M. Stöttinger and K. Divekar, “A Signature Based Architecture for Trojan Detection,” Proceedings of the 2014 ACM Workshop on Embedded Systems Security (WESS’14), October 2014. Presentation (pdf)

A. Heinig, V. Mooney, F. Schmoll, P. Marwedel, K. Palem and M. Engel, “Classification-based Improvement of Application Robustness and Quality of Service in Probabilistic Computer Systems,” Architecture of Computing Systems (ARCS 2012), March 2012, Winner of the ARCS 2012 Best Paper Award.

C. Dhoot, V. Mooney, S.R. Chowdhury and L.P. Chau, “Fault Tolerant Design for Low Power Hierarchical Search Motion Estimation Algorithms,” Proceedings of the IFIP Working Group 10.5 Very Large Scale Integration System-on-a-Chip (VLSI-SoC’11), October 2011. Presentation (pdf)

Z. Kedem, V. Mooney, K.K. Muntimadugu and K. Palem, “An Approach to Energy-Error Tradeoffs in Approximate Ripple Carry Adders,” Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED 2011), pp. 211-216, August 2011. Poster (pdf)

A. Singh, S. Mandavalli, V. Mooney and K.V. Ling, “A Novel and Fast Method for Characterizing Noise Based PCMOS Circuits,”

Proceedings of the Asian Symposium on Quality Electronic Design (ASQED 2011), July 2011. Presentation (pdf)

A. Gupta, S. Mandavalli, V. Mooney, K.V. Ling, A. Basu, H. Johan and B. Tandianus, “Low Power Probabilistic Floating Point Multiplier Design,” Proceedings of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI 2011), pp. 182-187, July 2011. Presentation (pdf)

C. Dhoot, V. Mooney, L.P. Chau and S.R. Chowdhury, “Low Power Motion Estimation with Probabilistic Motion Estimation,” Proceedings of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI 2011), pp. 176-181, July 2011.

A. Singh, A. Basu, K.V. Ling and V. Mooney, “Modeling Multi-output Filtering Effects in PCMOS,” Proceedings of the VLSI Design and Test Conference (VLSIDAT 2011), April 2011. Poster (pdf)

Z. Kedem, V. Mooney, K.K. Muntimadugu, K. Palem, A. Devarasetty and P.D. Parasuramuni, “Optimizing Energy to Minimize Errors in Dataflow Graphs Using Approximate Adders,” Proceedings of the International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES 2010), pp. 177-186, October 2010.

M. Lau, K.V. Ling, A. Bhanu and V. Mooney, “Error Rate Prediction for Probabilistic Circuits with More General Structures,” Proceedings of the 16th Workshop on Synthesis And System Integration of Mixed Information technologies (SASIMI’10), pp. 220-225, April 2010. Poster (pdf)

A. Bhanu, M. Lau, K. Ling, V. Mooney and A. Singh, “A More Precise Model of Noise Based CMOS Errors,” Proceedings of the 5th International Symposium on Electronic Design, Test and Applications (DELTA’10), pp. 99-102, January 2010. Poster (pdf)

K. Palem, A. Barr, A. Lingamneni, V. Mooney, R. Pingali, H. Sampath and J. Sivaswamy, I-Slate, “Ethnomathematics and Rural Education,” Proceedings of the IEEE Conference on Technologies for Humanitarian Challenges, August 2009.

F. Zhang, K. Szwaykowska, W. Wolf and V. Mooney, “Task Scheduling for Control Oriented Requirements for Cyber-Physical Systems,” Proceedings of the IEEE Real-Time Systems Symposium (RTSS’08), pp. 47-56, December 2008.

L. Zhao, D. Blough, V. Mooney and J. Fiore, “ An Approach Using the Data Distribution Service as the Connecting Transport for 100X Joint Battlespace Infosphere Servers,” High Performance Embedded Computing (HPEC’08), September 2008.

S. Kim and V. Mooney, “Sleepy Keeper: A New Approach to Low-Leakage Power VLSI Design,” Proceedings of the IFIP Working Group 10.5 Very Large Scale Integration System-on-a-Chip (VLSI-SoC’06), pp. 367-372, October 2006. Presentation (pdf)

J.C. Park and V. Mooney, “Pareto Points in SRAM Design Using the Sleepy Stack Approach,” Proceedings of the IFIP Working Group 10.5 Very Large Scale Integration System-on-a-Chip (VLSI-SoC’05), pp.239-244, October 2005. Presentation (pdf)

Y. Tan and V. Mooney, “WCRT Analysis for a Uniprocessor with a Unified Prioritized Cache,” Proceedings of the 2005 ACM SIGPLAN/SIGBED Conference on Languages, Compilers and Tools for Embedded Systems (LCTES’05), pp.175-182, June 2005. Presentation (pdf)

J. Lee and V. Mooney, “A novel O(n) Parallel Banker’s Algorithm for System-on-a-Chip,” Proceedings of the Asia and South Pacific Design Automation Conference (ASPDAC’05), pp.1304-1308, January 2005. Poster (pdf)

J.C. Park, V. Mooney and P. Pfeiffenberger, “Sleepy Stack Reduction in Leakage Power,” Proceedings of the International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS’04), pp.148-158, September 2004. Presentation (pdf)

J. Lee and V. Mooney, “A Novel Deadlock Avoidance Algorithm and Its Hardware Implementation,” Proceedings of the International Conference on Hardware/Software Codesign and System Synthesis (CODES-ISSS’04), pp.200-205, September 2004. Presentation (pdf)

Y. Tan and V. Mooney, “Integrated Intra- and Inter-Task Cache Analysis for Preemptive Multi-tasking Real-Time Systems,” Proceedings of 8th International Workshop on Software and Compilers for Embedded Systems (SCOPES’04), pp.182-199, September 2004. Presentation (pdf)

P. Kuacharoen, V. Mooney and V. Madisetti, “Efficient Execution of Large Applications on Portable and Wireless Clients,” Proceedings of the Mobility Conferences, August 2004.

K. Ryu, A. Talpasanu, V. Mooney and J. Davis, “Interconnect Delay Aware RTL Verilog Bus Architecture Generation for an SoC,” Proceedings of the IEEE Asia-Pacific Conference on Advanced System Integrated Circuits (AP-ASIC’04), pp.176-179, August 2004. Presentation (pdf)

O. Celebican, T. Simunic Rosing and V. Mooney, “Energy Estimation of Peripheral Devices in Embedded Systems,” Proceedings of the 2004 ACM Great Lakes Symposium on VLSI (GLVLSI’04), pp.430-435, April 2004. Poster (pdf)

Y. Tan and V. Mooney, “Timing Analysis for Preemptive Multi-Tasking Real-Time Systems with Caches,” Proceedings of the Design, Automation and Test in Europe Conference (DATE’04), pp.1034-1039, February 2004. Presentation (pdf)

A. Balasundaram, A. Pereira, J.C. Park and V. Mooney, “Golay and Wavelet Error Control Codes in VLSI,” Proceedings of the Asia and South Pacific Design Automation Conference (ASPDAC’04), pp.563-564, January 2004. Presentation (pdf) Poster (pdf)

B. E. S. Akgul, V. Mooney, H. Thane and P. Kuacharoen, “Hardware Support for Priority Inheritance,” Proceedings of the IEEE Real-Time Systems Symposium (RTSS’03), pp.246-254, December 2003. Presentation (pdf)

P. Kuacharoen, M. Shalan and V. Mooney, “A Configurable Hardware Scheduler for Real-Time Systems,” Proceedings of the International Conference on

Engineering of Reconfigurable Systems and Algorithms (ERSA’03), pp.96-101, June 2003. Presentation (pdf)

Y. Tan and V. Mooney, “A Prioritized Cache for Multi-tasking Real-Time Systems,” Proceedings of the 11th Workshop on Synthesis And System Integration of Mixed Information technologies (SASIMI’03), pp. 168-175, April 2003. Presentation (pdf)

M. Shalan, E. Shin and V. Mooney, “DX-Gt: Memory Management and Crossbar Switch Generator for Multiprocessor System-on-a-Chip,” Proceedings of the 11th Workshop on Synthesis And System Integration of Mixed Information technologies (SASIMI’03), pp. 357-364, April 2003. Presentation (pdf)

K. Ryu and V. Mooney, “Automated Bus Generation for Multiprocessor SoC

Design,” Proceedings of the Design Automation and Test in Europe Conference (DATE’03), pp. 282-287, March 2003. Presentation (pdf)

V. Mooney, “Hardware/Software Partitioning of Operating Systems,” Proceedings of the Design Automation and Test in Europe Conference (DATE’03), pp. 338-339, March 2003. Presentation (pdf)

P. Kuacharoen, V. Mooney and V. Madisetti, “Software Streaming via Block Streaming,” Proceedings of the Design Automation and Test in Europe Conference (DATE’03), pp. 912-917, March 2003. Presentation (pdf)

B. E. S. Akgul and V. Mooney, “PARLAK: Parametrized Lock Cache Generator,” Proceedings of the Design Automation and Test in Europe Conference (DATE’03), pp. 1138-1139, March 2003. Presentation (pdf)

J. Lee, V. Mooney, A. Daleby, K. Ingstrom, T. Klevin and L. Lindh, “A Comparison of the RTU Hardware RTOS with a Hardware/Software RTOS,” Proceedings of the Asia and South Pacific Design Automation Conference (ASPDAC’03), pp. 683-688, January 2003. Presentation (pdf)

J.C. Park, V. Mooney, K. Palem and K. Choi, “Energy Minimization of a Pipelined Processor using a low Voltage Pipelined Cache,” Proceedings of 36th Annual Asilomar Conference on Signals, Systems and Computers (ASILOMAR’02), pp. 67-73, November 2002. Presentation (pdf)

T. Akgul and V. J. Mooney, “Instruction-level Reverse Execution for Debugging,” Proceedings of the Workshop on Program Analysis for Software Tools and Engineering (PASTE’02), pp. 18-25, November 2002. Presentation (pdf)

E. Shin, V. Mooney and G. Riley, “Round-robin Arbiter Design and Generation,” Proceedings of the International Symposium on System Synthesis (ISSS’02), pp. 243-248, October 2002. Presentation (pdf)

K. Puttaswamy, K. Choi, J.C. Park, V. Mooney, A. Chatterjee and P. Ellervee, “System Level Power-Performance Trade-Offs in Embedded Systems Using Voltage and Frequency Scaling of Off-Chip Buses and Memory,” Proceedings of the International Symposium on System Synthesis (ISSS’02), pp. 225-230, October 2002. Presentation (pdf)

S. Srinivasan, J.C. Park and V. Mooney, “Combining Data Remapping and Voltage/Frequency Scaling of Second Level Memory for Energy Reduction in Embedded Systems,” Proceedings of the First International Workshop on Embedded System Codesign (ESCODES’02), pp. 57-62, September 2002. Presentation (pdf)

J. Lee, K. Ryu and V. Mooney, “A Framework for Automatic Generation of Configuration Files for a Custom Hardware/Software RTOS,” Proceedings of the International Conference

on Engineering of Reconfigurable Systems

and Algorithms (ERSA’02), pp. 31-37, June 2002. Presentation (pdf)

K. Palem, R. Rabbah, V. Mooney, P. Korkmaz and K. Puttaswamy, “Design Space Optimization of Embedded Memory Systems via Data Remapping,” Proceedings of the Joint Conference on Languages, Compilers, and Tools for Embedded Systems and Software and Compilers for Embedded Systems (LCTES’02-SCOPES-02), pp. 28-37, June 2002. Presentation (pdf)

M. Shalan and V. Mooney, “Hardware Support for Real-Time Embedded Multiprocessor System-on-a-Chip Memory Management,” Proceedings of the Tenth International Symposium on Hardware/Software Codesign (CODES’02), pp. 79-84, May 2002. Presentation (pdf)

L.Chakrapani, P. Korkmaz, V. Mooney, K. Palem, K. Puttaswamy and W. Wong, “The Emerging Power Crisis in Embedded Processors: What can a (poor) Compiler do?,” Proceedings of the International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES’01), pp. 176-180, November 2001. Presentation (pdf)

B. E. S. Akgul, J. Lee and V. Mooney, “A System-on-a-Chip Lock Cache with Task Preemption Support,” Proceedings of the International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES’01), pp. 149-157, November 2001. Presentation (pdf)

T. Akgul, P. Kuacharoen, V. Mooney and V. Madisetti, “A Debugger RTOS for Embedded Systems,” Proceedings of the 27th EUROMICRO Conference (EUROMICRO’01), pp. 264-269, September 2001. Presentation (pdf)

P. Kuacharoen, T. Akgul, V. Mooney and V. Madisetti, “Adaptability, Extensibility, and Flexibility in Real-Time Operating Systems,” Proceedings of the EUROMICRO Symposium on Digital Systems Design (EUROMICRO’01), pp. 400-405, September 2001. Presentation (pdf)

K. Ryu, E. Shin and V. Mooney, “A Comparison of Five Different Multiprocessor SoC Bus Architectures,” Proceedings of the EUROMICRO Symposium on Digital Systems Design (EUROMICRO’01), pp. 202-209, September 2001. Presentation (pdf)

P. Shiu, Y. Tan and V. Mooney, “A Novel Parallel Deadlock Detection Algorithm and Architecture,” 9th International Workshop on Hardware/Software Codesign (CODES’01), pp. 30-36, April 2001. Presentation (pdf)

B. E. Saglam (Akgul) and V. Mooney, “System-on-a-Chip Processor Synchronization Support in Hardware,” Proceedings of the Design, Automation and Test in Europe Conference (DATE’01), pp. 633-639, March 2001. Presentation (pdf)

M. Shalan and V. Mooney, “A Dynamic Memory Management Unit for Embedded Real-Time System-on-a-Chip,” International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES’00), pp. 180-186, November 2000. Presentation (pdf)

V. Mooney, “Path-Based Edge Activation for Dynamic Run-Time Scheduling,”International Symposium on System Synthesis (ISSS’99), pp. 30-36, November 1999. Presentation (pdf)

V. Mooney, D. Ruspini, O. Khatib and G. De Micheli, “Hardware-Software Run-Time Systems and Robotics: A Case Study,” Euromicro Conference, pp. 162-167, Vasteras, Sweden, August 1998.

V. Mooney and G. De Micheli, “Real Time Analysis and Priority Scheduler Generation for Hardware-Software Systems with a Synthesized Run-Time System,” International Conference on Computer-Aided Design (ICCAD’97), pp. 605-612, November 1997.

V. Mooney, T. Sakamoto and G. De Micheli, “Run-Time Scheduler Synthesis For Hardware-Software Systems and Application to Robot Control Design,” 5th International Workshop on Hardware/Software Codesign (CODES’97), pp. 95-99, March 1997.

V. Mooney, C. Coelho, T. Sakamoto and G. De Micheli, “Synthesis From Mixed Descriptions,” European Design Automation Conference, pp. 114-119, September 1996.

V. Mooney, C.Coelho and G. De Micheli, “A Multiple Paradigm Front-End for Hardware-Software Synthesis,” HILES Workshop, November 1995.

C. Coelho, J. Yang, V. Mooney and G. De Micheli, “Redesigning Hardware-Software Systems,” Third International Workshop on Hardware/Software Codesign (CODES’94), pp. 116-123, September 1994.

Keynote Presentations

V. Mooney, “Research Trends in Hardware/Software Codesign of Embedded Operating Systems for FPGAs,” FPGAworld Conference, Stockholm, Sweden, September 2007.

V. Mooney, “Design of a Hardware/Software RTOS for FPGAs with Processors,” FPGAworld Conference, Vasteras, Sweden, September 2004.

Technical Reports

Z. Kedem, V. Mooney, K. Muntimadugu and K. Palem, “Optimizing Energy to Minimize Errors in Approximate Ripple Carry Adders,” Technical Report TR11-02, Rice University, 2011.

V. Mooney, K. Palem and R. Wunderlich, “Loss-Tolerant and Secure Embedded Computing via Inscrutable Instruction-Set Architectures (I2SA),” Technical Report GIT-CC-04-12, Georgia Institute of Technology, 2004.

Y. Tan and V.Mooney, “Cache-Related Timing Analysis for Multi-tasking Real-Time Systems with Nested Preemptions,” Technical Report GIT-CC-04-11, Georgia Institute of Technology, 2004.

P. Pfeiffenberger, J.C. Park and V. Mooney, “Some Layouts Using the Sleepy Stack Approach,” Technical Report GIT-CC-04-05, Georgia Institute of Technology, June 2004.

Y. Tan and V. Mooney, “Timing Analysis for Preemptive Multi-tasking Real-Time Systems with Caches,” Technical Report GIT-CC-04-02, Georgia Institute of Technology, February 2004.

A. Balasundaram, A. Pereira, J.C. Park and V. Mooney, “Golay and Wavelet Error Control Codes in VLSI,” Technical Report GIT-CC-03-33, Georgia Institute of Technology, December 2003.

J. Lee and V. Mooney, “An O(min(m,n)) Parallel Deadlock Detection Algorithm,” Technical Report GIT-CC-03-41, Georgia Institute of Technology, September 2003.

K Ryu and V. Mooney, “Automated Bus Generation for Multiprocessor SoC Design,” Technical Report GIT-CC-02-64, Georgia Institute of Technology, December 2002.

T. Akgul and V. J. Mooney, “Instruction-level Reverse Execution for Debugging,” Technical Report GIT-CC-02-49, Georgia Institute of Technology, September 2002.

E. Shin, V. Mooney and G. Riley, “Round-robin Arbiter Design and Generation,” Technical Report GIT-CC-02-38, Georgia Institute of Technology, July 2002.

R. Banakar, M. Ekpanyopang, K. Puttaswamy, R. Rabbah, M. Balakrishnan, V. Mooney and K. Palem, “An Access based Energy Model for the Datapath and Memory Hierarchy of HPL-PD Microarchitecture in Trimaran Framework (TRIREME),” Technical Report GIT-CC-02-35, Georgia Institute of Technology, June 2002.

D. Sun, D. Blough and V. Mooney, “Atalanta: A New Multiprocessor RTOS Kernel for System-on-a-Chip Applications,” Technical Report GIT-CC-02-19, Georgia Institute of Technology, April 2002.

K. Palem, R. Rabbah, V. Mooney, P. Korkmaz and K. Puttaswamy, “Power Optimization of Embedded Memory Systems via Data Remapping,” Technical Report GIT-CC-02-11, Georgia Institute of Technology, February 2002.

V. Mooney and G. De Micheli, “Hardware/Software Codesign of Run-Time Schedulers for Real-Time Systems,” Technical Report CSL-TR-97-739, Stanford Computer Science Department Electronic Library, November 1997. (This is an early version of the journal paper by the same title in Design Automation of Embedded Systems, 1999).

V. Mooney, “Searle’s Chinese Room and its Aftermath,” Center for the Study of Language and Information, CSLI-97-202,” June 1997.

Unpublished Papers

“Verilog Simulation of a Hardware-Software Implementation of a Robotics Control Algorithms,” F. Abdullah and V. Mooney, January 28, 1998.

Any suggestions, questions or concerns can be addressed to

Vincent Mooney.